# Paving the Way for NFV Acceleration: A Taxonomy, Survey and Future Directions

XINCAI FEI, FANGMING LIU (CORRESPONDING AUTHOR), QIXIA ZHANG, and HAI JIN, National Engineering Research Center for Big Data Technology and System, Key Laboratory of Services Computing Technology and System, Ministry of Education, School of Computer Science and Technology, Huazhong University of Science and Technology, China HONGXIN HU, Clemson University, USA

HONGAIN HU, Clemson University, USA

As a recent innovation, network functions virtualization (NFV), with its core concept of replacing hardware middleboxes with software network functions (NFs) implemented in commodity servers, promises cost savings and flexibility benefits. However, transitioning NFs from special-purpose hardware to commodity servers has turned out to be more challenging than expected, as it inevitably incurs performance penalties due to bottlenecks in both software and hardware. To achieve performance comparable to hardware middleboxes, there is a strong demand for a speedup in NF processing, which plays a crucial role in the success of NFV. In this article, we study the performance challenges that exist in general-purpose servers and simultaneously summarize the typical performance bottlenecks in NFV. Through reviewing the progress in the field of *NFV acceleration*, we present a new taxonomy of the state-of-the-art efforts according to various acceleration approaches. We discuss the products, solutions and projects emerged in industry. We also present a gap analysis to improve current solutions and highlight promising research trends that can be explored in the future.

$\label{eq:ccs} \texttt{CCS Concepts:} \bullet \textbf{Computer systems organization} \rightarrow \textbf{Network Functions Virtualization}; \textit{NFV Acceleration}; \bullet \textbf{Networks} \rightarrow \texttt{Carrier Networks};$

Additional Key Words and Phrases: Network Functions Virtualization, NFV acceleration, high performance

# ACM Reference Format:

Xincai Fei, Fangming Liu (corresponding author), Qixia Zhang, Hai Jin, and Hongxin Hu. 2020. Paving the Way for NFV Acceleration: A Taxonomy, Survey and Future Directions. *ACM Comput. Surv.* 1, 1, Article 1 (January 2020), 40 pages. https://doi.org/10.1145/3397022

# **1 INTRODUCTION**

Modern networks are becoming more sophisticated with the ubiquitous deployment of hardwarebased network functions (NFs), also known as middleboxes [128]. These middleboxes play a key role in advanced traffic processing and provide a variety of network functionalities, from firewalls and intrusion detection systems for improving security to proxies and WAN optimizers for enhancing performance. Traditionally, middleboxes are usually tightly coupled with dedicated hardware. When launching a new service, more pieces of hardware are needed, which leads to a long service deployment cycle. With more capital investment and shorter hardware lifecycles, network operators face a severe situation of substantially lower profits, since launching new services is difficult and time-consuming.

Authors' addresses: Xincai Fei, god14fei@hust.edu.cn; Fangming Liu (corresponding author), fmliu@hust.edu.cn; Qixia Zhang, zhangqixia427@hust.edu.cn; Hai Jin, hjin@hust.edu.cn, National Engineering Research Center for Big Data Technology and System, Key Laboratory of Services Computing Technology and System, Ministry of Education, School of Computer Science and Technology, Huazhong University of Science and Technology, 1037 Luoyu Rd, Wuhan, Hubei, 430074, China; Hongxin Hu, Clemson University, Clemson, SC 29634, Clemson, South Carolina, 29631, USA, hongxih@clemson.edu.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

© 2020 Association for Computing Machinery.

0360-0300/2020/1-ART1 \$15.00

https://doi.org/10.1145/3397022

Network functions virtualization (NFV) is a novel paradigm for offering flexible network services, by leveraging virtualization technologies to decouple NFs from hardware middleboxes and make them execute in virtual machines (VMs), containers, or even natively. By this means, NFV abstracts general-purpose hardware (e.g., x86 servers) and brings considerable benefits: 1) reduced costs in purchasing regular commercial off-the-shelf (COTS) hardware instead of dedicated network equipment; 2) shortened time-to-market to deploy new network services and increased profits from these new services; 3) greater flexibility to scale up or down software-based NFs in an on-demand basis and migrate NFs to various locations whenever necessary; and 4) higher efficiencies in power, cooling and finding space for launching new network services. Based on a report by Global Market Insights company, the NFV market share will exceed 70 billion US dollars by 2024 [42].

Although NFV introduces substantial benefits, it is still challenging to put the deployment of software-based NFs into practice. One of the major obstacles is the difficulty in achieving high performance comparable to hardware-based middleboxes when running software NFs in a virtualized environment. For example, the processing delay of fully virtualized gateways results in a maximum of 132  $\mu$ s, which is almost 8 times larger than the processing delay of decomposed gateways (i.e., 15  $\mu$ s) [13]. In fact, it is vital for many NFV-based applications to achieve the desired performance. For instance, Voice over Internet Protocol services are particularly delay-sensitive and often require less than 150 milliseconds (ms) of end-to-end latency with low latency variance (i.e., jitter) [24]. Even a transient lack of connection can cause service disruption and thus violate the service level agreements (SLAs). For throughput-sensitive applications, Internet Protocol version 4 (IPv4) and Internet Protocol version 6 (IPv6) forwarding need to support 10 million of packets per second (Mpps) [1] for providing high performance and scalability. In addition, a high-performance IP security (IPsec) stack requires to sustain more than 190 gigabits per second (Gbps) of encrypted traffic on a single server [63]. Therefore, NFV solutions need to be carefully designed to satisfy the strict performance requirements of different applications.

As technology advances, modern commodity servers are generally equipped with multiple CPU cores, thus allowing workloads running on processors in parallel. Meanwhile, the fast development of high-speed network enables network interface cards (NICs) to evolve from 10 Gbps to 100 Gbps [72]. However, these advances do not guarantee high performance for NFV applications. The fundamental reason behind this is that the operating system's (OS) networking stack is not designed for fast middlebox processing but for general-purpose communications. Indeed, achieving high-performance packet processing from commodity servers is challenging and has been a hot research topic in both academia and industry (e.g., ETSI works [44–48]) for several years. In many cases, it is hardly possible to achieve the desired performance due to the following obstacles that are inherent in both software and hardware, which cumulatively slow down the packet processing in commodity servers and hinder high performance in NFV:

- 1) After the speed of NICs transiting from 10 Gbps to 100 Gbps, the processing time of each packet on the network links decreases from 67 nanoseconds (ns) to only 6.7 ns for the minimum 64B packet, in order to sustain line rate [90]. This imposes great pressure on the NFV system architectures, which will inevitably get worse in the case of a 100-gigabit interface [71].

- 2) General-purpose network stacks, such as the Linux network stack, lack optimized kernel-user space and fast input/output (I/O) data path for software packet processing. In fact, modern OSes can result in 10 to 20 times the speed slower than a 10-gigabit interface to process a packet for an application [20]. High cost induced from numerous user-kernel context switches and system call interruptions turn out to be the major performance bottlenecks for yielding high performance [74, 90].

- 3) Popular software switches, such as Open vSwitch [36, 112], which are used by (i) hypervisors, such as Kernel-based VM (KVM) [83], to interconnect VMs and/or (ii) bare metal deployments to interconnect containers (e.g., Docker), are incapable of providing desired performance. The reasons would be the inefficiencies of the software switch, the bottlenecks exist in virtualized network device drivers (e.g., virtio [123]), and inter-core communications for traffic steering.

- 4) Some existing NFV frameworks (see Section 4.4) do not fully exploit low-level hardware features, such as cache consistency in a 3-hierarchy style and memory concurrency, in order to improve

the cache hit and decrease the memory-access overhead. Besides, the capabilities of modern NICs are also not fully utilized, since they can not only do simple hashing of packets (e.g., Receive Side Scaling [27]) but also provide both packet classification and dispatching capabilities (e.g., Flow Director [58]). Fortunately, these problems are recently solved by Metron [72].

In the context of NFV, traffic usually needs to go through a sequence of NFs in a specific order, which is also known as service function chain (SFC), or service chaining [66]. Accordingly, it needs multiple VMs (or containers) to create a single network service, and those VMs could reside in the same or different servers. Traffic among VMs has to flow back and forth among different guest OSes within the same or different hosts (servers). The latter case brings a greater challenge for sustaining high performance, compared to service chains within a single server where packet processing incurs lower delay and consumes fewer CPU resources than going through the NICs [106].

To address the performance issues described above, a growing number of research efforts have been paid to improve NFV performance. Specifically, NFs are possible to achieve prominent performance improvement in an NFV platform by some forms of acceleration. Through a careful review of the progress in this field, we present a new taxonomy regarding all the surveyed works based on various acceleration approaches. We further discuss these works in detail and reveal their respective advantages and disadvantages in each category.

In this article, both acceleration of NFV and packet delivery for specific NFs (e.g., software switches and routers) are considered as the survey topic. Although Cerović et al. [20] have already written a related survey, many NFV-specific acceleration works are missing in their work since their major focus is on packet processing. In contrast, we focus on NFV acceleration and our work provides comprehensive reviews on the typical performance challenges in the context of NFV. We present a new taxonomy regarding a wide spectrum of NFV acceleration categories, while [20] just classifies the approaches into hardware- or software-based implementations and does not discuss some important aspects (e.g., NF offloading on smart NICs). We also discuss industrial products and solutions that are lacking in [20], which indicate the feasibility of NFV acceleration into practical applications. Other works just focus on only one aspect, such as I/O frameworks [38] or NFV datapath [86]. Besides, we present a gap analysis in order to improve the current solutions and introduce some promising research trends that can be explored in the future.

The roadmap of this article is organized as follows. In Section 2, we introduce the performance metrics of interest, take a close look into the typical performance bottlenecks in NFV and analyze the associated performance challenges. Next, we introduce some common frameworks, software switches/routers, and hardware accelerators used in the field of NFV acceleration in Section 3. In Section 4, we provide a taxonomy regarding the state-of-the-art approaches in this field. We survey these works in each category from Section 4.1 to Section 4.4, respectively. Then we briefly give a discussion and comparison of the surveyed works in Section 4.5. In Section 5, we discuss the emerging products, solutions and popular projects in industry. We present a gap analysis and highlight promising future trends in Section 6. Finally, Section 7 summarizes and concludes this article.

#### 2 PERFORMANCE METRICS, BOTTLENECKS AND CHALLENGES IN NFV

In this section, we introduce the performance metrics of interest, and study and summarize the bottlenecks and challenges that affect the performance of NFV.

### 2.1 Performance Metrics of Interest

In an NFV platform, network performance is the analysis and review of collective statistics and metrics, in order to reflect the quality of network services. Broadly, there are multiple means to measure the performance in the context of NFV, as each service chain has different SLAs. Among the available options, the following performance metrics of interest are often considered as fundamental.

• Raw interface throughput describes the total amount of traffic that can be transferred over an I/O device such as a NIC over time, which is usually measured in megabits or gigabits per

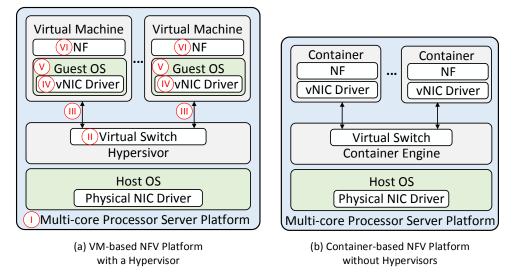

Fig. 1. Typical NFV performance bottlenecks.

second (i.e., Mbit/s or Gbit/s). This metric is used to weigh the processing speed of a physical network interface and is limited by the maximum interface bandwidth.

- **Packet throughput** describes how fast an I/O system can process packets, which is usually measured in millions of packets per second (i.e., Mpps). This metric is used to weigh the packet forwarding speed of a NIC and has much to do with the packet size. Generally, the smaller the packet size is, the greater the challenge is imposed on packet throughput.

- End-to-end latency is usually measured from a source that generates the traffic and to a sink that receives the traffic. The end-to-end latency can be further classified into four types of delays, i.e., processing delay to handle packets on a node, queuing delay to buffer packets before sending them out, transmission delay to push packets onto a link, and propagation delay to deliver packets through the link.

Even though both raw interface throughput and packet throughput can describe the throughput, the former reflects the data transmission speed through an interface, while the latter reflects how many packets of the same size can be transferred per second. Note that some surveyed works need to measure the throughput under different packet sizes, in this case, packet throughput is more intuitive for evaluation. Besides, other metrics such as packet loss rate and the latency variance, also known as jitter, can also be used to measure the network performance. Since most of the surveyed works evaluate their systems via throughput or latency, we mainly discuss the three listed metrics above in this paper.

# 2.2 Typical Performance Bottlenecks

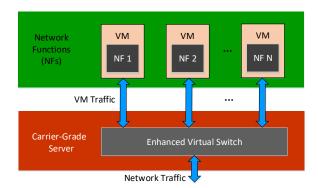

NFV advocates to use software-based NFs implemented in commodity servers. Multiple NFs are often consolidated into a single server, where each NF runs on a VM basis in a virtualized environment. As such, a typical NFV platform is generally composed of some fundamental components such as host OS, virtual switches, virtual NICs and NFs. An NFV platform can run NFs in VMs or containers, or even run them as native processes. There are two typical NFV platforms (i.e., with/without hypervisors), both of which are plotted in Figure 1. Here we first focus on the performance bottlenecks in a VM-based NFV platform with a hypervisor, where the general location of each kind of performance bottleneck is shown in Figure 1(a). These bottlenecks can be categorized into six kinds, from the server hardware bottleneck to NF bottleneck. Note that some bottlenecks are not unique to virtualized environments, however, these bottlenecks would accumulate as NFV is adopted. We now give a closer examination on how these bottlenecks occur from a systematic view.

Paving the Way for NFV Acceleration: A Taxonomy, Survey and Future Directions

- I. **Server Hardware Bottleneck.** As a whole, the server hardware characteristics greatly affect the performance of NFs running on it. Typical server parameters can be the number of cores, CPU frequency, cache size, memory size and latency, bandwidth of peripheral buses, NIC speed, instruction set, etc. An NFV platform usually requires to be equipped with powerful servers (e.g., Intel Xeon E5 v4 series processors with up to 22 cores, 44 threads, 55 MB LLC, 40 GbE NIC, and Intel Xeon E7 v4 series processors with up to 24 cores, 48 threads, 60 MB LLC, 40 GbE NIC) to eliminate server hardware bottleneck.

- II. **Virtual Switch Bottleneck.** The virtual switch bottleneck is obvious since the virtual switch on the hypervisor can be viewed as an intermediate stop, through which all packets must go, no matter packets travel into and out of a host, or packets flow between VMs. The capability of the virtual switch plays a crucial role in a high-performance NFV platform.

- III. Communication Bottleneck. The communication bottleneck between the guest and host OS arises from double memory page translation and interrupt remapping, etc., between virtual hardware resources and physical hardware resources. The virtual CPUs in the guest OS run as QEMU [15] threads which are treated as normal processes in the host OS. These threads can be scheduled in any physical core in the host which increases cache misses and hampers the performance. This results in that some unnecessary OS features may also introduce high cost that limits the performance. For instance, the task scheduling mechanism of the OS is good for a fair CPU utilization among the processes; however, for NF processing that requires high performance, it fails and may lead to high context switches due to the fair CPU shares.

- IV. I/O Device Bottleneck. The I/O device bottleneck comes with the virtual NIC drivers. It incurs overheads due to the high overhead of delivering packets between guest VMs and I/O device driver, since the driver cannot directly access the memory where a packet lies in the guest VM. Effective memory sharing mechanism should be provided by the driver for accessing the packet. For example, virtio [123] is a major virtualization standard for network device drivers and has been adopted by many NFV solutions; however, it is slow since the hypervisor has to emulate actual physical NICs, and this emulation is both complicated and inefficient.

- V. **Guest OS Bottleneck.** The guest OS bottleneck is similar to the bottleneck that exists in a non-virtualized environment. The packet processing in a traditional networking stack often incurs heavy kernel-user space context switches. Besides, the costly system call interruption for awakening the virtual CPU to handle the arrival packets further penalizes the performance.

- VI. **NF Bottleneck.** The NF bottleneck occurs due to inefficient software design. NF design concerns whether all capabilities offered by the server hardware can be leveraged. Software features such as pipelining, multi-threading and deadlock avoidance should be carefully considered in the design of a new NF. With regard to exploiting the hardware architecture, deterministic allocation of CPUs can improve the performance of some NFs, since threads in CPUs may communicate with each other and benefit from sharing the same cache (improved cache hit ratio) when they need to exchange information. Furthermore, NFs can get faster access to the memory that is close to the CPU in which the thread is running than the memory connected to remote CPUs. For those NFs that need high throughput performance and frequent memory access, these software features need to be carefully integrated into the NF design.

As compared with the heavy-weight VM-based NFV platforms, container-based NFV platforms (e.g., Docker) can implement NFs as standard user-space processes inside lightweight container instances, which can be quickly started while incurring little overhead. In this way, more NFs or application instances can run in containers with fewer resource consumption, lower system overhead and higher performance as compared with VMs. However, container-based NFV platforms also have some performance bottlenecks, such as the server hardware bottleneck, the communication bottleneck, the NF bottleneck, etc. As plotted in Figure 1(b), since there is no hypervisor in container-based NFV platforms, all the container instances share the same host OS along with its hardware resources. Thus, the performance isolation in containers is not as strict as hypervisor-based platforms with fully virtualized hardware resources. In other words, containers are more fragile when facing Kernel attacks. For instance, an attacker can use some non-namespace resources in Docker containers to access the host OS. In this case, the container under attack may occupy

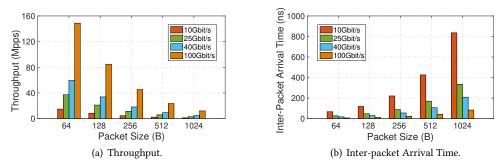

Fig. 2. The packet throughput and inter-packet arrival time under different packet sizes and interface bandwidths.

the entire host's resources, which will severely affect the operation of other containers and their running NFs. Performance isolation in container-based environments can also be broken by the large computation overhead related to the network stack [75]. As a matter of fact, containers with high traffic rates can cause the performance of co-located computing-driven containers to suffer an almost 6x slowdown. Besides, how to split microservices in container-based NFV platforms and how to efficiently communicate with other microservices will both affect the performance.

Due to numerous layers of bottlenecks in both software and hardware accumulated to the NFV platform, current NF deployments are just in small test scale, while large-scale NF deployments are severely limited. Though many high-performance software frameworks have been employed to address some performance issues via bypassing networking stacks, the accelerated guests only guarantee fast packet processing for specific NFs and the accelerated virtual switch still requires to copy packets between the hypervisor and the guest's memory in VM-based NFV platforms. Recent research finds that the PCI Express (PCIe), which is the interconnection between the host and device drivers, can also become the performance bottleneck even in combination with optimized I/O frameworks, since it has side effects on both throughput and latency of network applications [102]. For a high-performance service chain, there still exist a number of hindrances in the NFV platform, especially enabling high-speed communication between two guests or between host and guest. When a service chain is deployed in two or more NFV platforms, achieving this target will become more challenging.

### 2.3 Performance Challenges

For an NFV system that is designed for carrier networks, NF deployments often need to provide throughput with the order of tens of Gbps and latency with the order of tens of µs [108], in order to meet the strict performance requirements. With the development of NICs, there is a strong demand for higher packet processing speed. This, however, imposes great challenges on the platform to reach the theoretical upper bound of forwarding packets. To demonstrate this truth, Figure 2 shows the packet forwarding rates (throughput) and inter-packet arrival time under different packet sizes and interface bandwidths. As plotted in the figure, while the packet forwarding rate increases from 14.88 Mpps to 59.52 Mpps, the inter-packet arrival time drops from 67.2 ns to 16.8 ns when the interface bandwidth increases from 10 Gbps to 40 Gbps for 64B packet. Katsikas et al. [71] even declare that the per-packet time to process 64B packets at 40 Gbps is only 12.8 ns. To sustain the maximum packet forwarding rate, shorter inter-packet arrival time means fewer cycles that a CPU is allowed to process a packet.

Modern multi-core processors are common to adopt a multi-level cache design. Specifically, each CPU core has its dedicated L1 cache and L2 cache, but the last level cache (LLC) is shared among the cores of the same CPU socket. This multi-level cache architecture can largely reduce the CPU cycles for memory access. Note that both LLC and dynamic random access memory (DRAM) have local access and remote access. Beside, non-uniform memory access (NUMA) architecture is also common in modern multi-core systems to separate memory for different processors, where the

| Data Source                            | Latency        |

|----------------------------------------|----------------|

| L1 cache hit                           | 4 cycles       |

| L2 cache hit                           | 12 cycles      |

| LLC hit, unshared line                 | 26-31 cycles   |

| LLC hit, shared line in another core   | 65 cycles      |

| LLC hit, modified line in another core | 75 cycles      |

| Remote LLC                             | 100-300 cycles |

| Local DRAM                             | 60 ns          |

| Remote DRAM                            | 100 ns         |

Table 1. Latency of memory access on Intel Xeon 5500 processor [87].

memory access time is proportional to the distance between the memory and the processor. In a NUMA-based system, accessing a processor's local memory is much faster than accessing remote memory (i.e., memory shared among processors or memory local to another processor).

Table 1 summarizes the latency of memory access with different data sources on a NUMA-based architecture with two Intel Xeon 5500 processors (each with 256 KB L2 cache and 8 MB shared LLC among 4 cores), which are based on the same microarchitecture as Intel Core i7 processor [87]. This processor architecture also brings a huge difference in processing packets, especially for packets with small sizes. For instance, the inter-arrival time of 64B packets is 12.8 ns at 40 Gbps, which allows a CPU to process the packets in 33 cycles with the main frequency of CPU at 2.6 GHz. Considering that both receiving or sending a packet and table lookup need memory access, it is still hard to sustain maximum packet forwarding rate within 33 cycles, only if LLC can hit in every memory access with a maximum latency of 31 cycles. If LLC misses, packets via remote DRAM require up to 100 ns. Even though superior processors like Intel Xeon E5 v4 processors allow direct data transfer to LLC with optimized LLC-to-core communications and Intel Xeon E7 v4 processors even increase the LLC by 60 MB (up to 2.5 MB per core), it is still challenging to reach theoretical packet forwarding rate in case that LLC misses.

In the context of NFV, multiple NFs are often running in a single server. However, in fact, few state-of-the-art packet processing schemes can guarantee that packets are delivered to the right core straight from the NIC. They either suffer from inefficient inter-core packet transfers among NFs or unbalanced workload among CPU cores [72]. One existing work, Metron [72] can process packets potentially at L1 cache speeds. In particular, Metron offloads part of the packet processing logic to the network to eliminate inter-core transfer and handles the remaining packets with tag-based hardware dispatching so as to achieve a potential L1 cache speed for processing them. Assisted with commodity hardware, Metron can process deep packet inspection at the speed of 40 Gbps and realize stateful NFs at the speed of a 100 GbE network card on a single server. However, it inherits the limitations of SNF [73], which makes it only applicable to fairly limited service chains. In short, considering that only a few tens of CPU cycles are available for each packet at 100 Gbps, it is a huge challenge for achieving either high throughput or low latency of NF chains.

# 3 COMMON SOFTWARE FRAMEWORKS, SWITCHES/ROUTERS AND HARDWARE FOR NFV ACCELERATION

Before investigating the state-of-the-art approaches in the field of NFV acceleration, we first give a general understanding of some necessary prerequisites. In this section, we briefly introduce the software frameworks, software switches/routers and popular hardware that are commonly associated with NFV acceleration.

## 3.1 Software I/O frameworks and Switches/Routers

High-performance software frameworks have been developed to provide high packet I/O speed since several years ago. Until now, the most popular examples are Intel Data Plane Development Kit (DPDK) [29], netmap [118], PF\_RING [103] and PF\_RING DNA (Direct NIC Access) [119], Snabb [107], and OpenOnload [129]. These frameworks achieve performance improvements either via

bypassing the OS kernel and running applications in user space or sharing memory buffers that can be accessed by both kernel and applications [9, 116]. There are some software switches that run on top of a network I/O framework, such as VALE switch [120] and OvS-DPDK [41]. We also discuss some popular software switches (or routers) such as Open vSwitch (OvS) [36, 112], Berkeley Extensible Software Switch (BESS) [50] (a.k.a., SoftNIC [51]), and Click Modular Router [78]. Table 2 summarizes the general information of these frameworks and switches/routers.

**DPDK.** DPDK consists of a collection of data plane libraries and NIC drivers for high-speed packet processing. By calling DPDK libraries and application program interfaces (APIs) in the user space, applications continuously poll instead of handling interrupts for each arrived packet. In this way, the overheads inherent in traditional networking stack can be eliminated. DPDK also implements a set of optimizations including lock-free rings, thread affinity, NUMA awareness, and huge page setting. In particular, the lock-free rings in DPDK are based on the Linux kernel lock-free ring buffers to reduce locking overhead, which supports both one-to-one and many-tomany producer/consumer models. Thread affinity means that DPDK binds threads to logical cores to reduce context switches across cores and increase CPU cache hit rate. DPDK also implements per-core memory in NUMA to deal with cache consistency and uses 2 MB and 1 GB huge pages to reduce the case that translation lookaside buffer (TLB) misses. DPDK maintains hardware independence since it provides a programming framework for any processors. DPDK can boost the packet processing performance by 10 times, reaching more than 80 Mpps throughput by using a single processor [57]. However, the CPU overhead is not reduced since DPDK Poll Mode Drivers (PMDs) run in busy loops by constantly scanning either physical NIC ports on the host or vNIC ports in guests for the arrival of packets.

**netmap.** Netmap is a high-performance framework for packet I/O. It reduces or eliminates substantial overheads such as per-packet memory allocations, system calls and packet copying by introducing three optimization techniques, i.e., buffer preallocation, use of large batches and shared buffers. All of these are for fast transmission of packets through the NIC to applications in the user space. Note that netmap has two modes to allow users to decide whether packets should go through the host stack or not [20], while the netmap mode allows packets to be directly delivered to an application through the netmap API. The implementation of netmap brings minor modifications and does not depend on special hardware. According to [118], netmap can easily reach line rate on a 10G NIC with 64B frame size.

**P4.** P4 [16] is a high-level programming language used for protocol-independent packet processors, which can work as a general, flexible interface between the switches and the controller for matching header fields and parsing packets. A simple API is provided by P4 for connecting the actual hardware implementation of the switch. In short, P4 can achieve three goals: protocol independence (i.e., switches should be able to handle packets of different formats), reconfigurability (i.e., the controller can redefine how to parse and process packets) and target independence (i.e., programmers can describe the functions to process packets without knowing the details of hardware implementation). As compared with commonly-used programming languages (e.g., C or Python), P4 is a domain-specific language, which provides high-level abstraction for network programming and optimizes network data forwarding through a set of carefully-designed constructs.

**PF\_RING (DNA).** PF\_RING is an efficient packet capture technology based on the Linux kernel [5]. The core solution of PF\_RING is to decrease the copy time during the transmission processes of packets. To this end, PF\_RING polls packets from the NIC to ring buffers, and then the user-space applications read packets directly from the rings, by means of utilizing Linux New API (NAPI). However, this mechanism has to experience two polling periods for both NAPI and the application, and consumes extra CPU cycles. To reduce CPU consumption for polling packets, PF\_RING DNA copies packets from the NIC to ring buffers by NIC NPU instead of NAPI. It has better performance but the disadvantage is that only one application has access to the ring at a time and applications need to exchange for each other to distribute incoming packets.

**Snabb.** Snabb is a fast packet processing toolkit written in the scripting language Lua. It allows developers to add functionality to the Snabb stack by loading modules into the Snabb engine, which makes Snabb extensible. These modules can be Lua or other native code objectives, which are

| Framework        | Begin time | Organization       | Description                               |

|------------------|------------|--------------------|-------------------------------------------|

| DPDK             | 2012       | DPDK               | A set of data plane libraries and drivers |

| netmap           | 2012       | Universita di Pisa | A high-performance network I/O framework  |

| P4               | 2014       | P4 Language        | A language for programming protocol-      |

|                  | 2014       | Consortium         | independent packet processors             |

| PF_RING (DNA)    | 1998       | Ntop Team          | A new type of network socket              |

| Snabb            | 2012       | Snabb Lab          | An extensible networking toolkit          |

| OpenOnload       | 2008       | Solarflare         | A high-performance network stack          |

| Switches/Routers | Begin time | Organization       | Description                               |

| VALE switch      | 2012       | Universita di Pisa | A software Virtual Local Ethernet         |

| OvS-DPDK         | 2014       | Linux Foundation   | DPDK accelerated OvS                      |

| OvS              | 2012       | Linux Foundation   | An open-source virtual switch             |

| BESS             | 2015       | Berkeley           | A modular and software switch             |

| Click            | 2000       | MIT                | A modular and software router             |

Table 2. Common software I/O frameworks and switches/routers.

named as libraries and *Apps*, respectively. A specific application is modeled as an App network, and the Apps can be very simple or complex operations in NFs. As a result, developers can build customized software packet processing network by resembling reusable Apps. Snabb supports NFV as it allows fast data exchange between VMs and provides user-space drivers similar to DPDK.

**OpenOnload.** OpenOnload is a high-performance framework that not only significantly reduces latency and CPU utilization, but also increases packet rate and bandwidth [129]. It runs on standard Linux and requires no modifications to applications. Its high performance partly stems from detouring the OS stack so that the packet processing can be fully performed at user space. Note that OpenOnload is a hybrid stack, which allows applications to flexibly run either at user space or kernel space for any traffic to choose, whichever is appropriate. Applications using OpenOnload typically see a 4-time improvement in message rates.

The following is an introduction to the software switches or routers in the literature.

**VALE switch.** VALE is a software Virtual Local Ethernet. The ports on VALE can communicate using the netmap API. It is designed to be used to interconnect multiple VMs, working as a learning bridge in the host. It can achieve very high-speed communication between different types of VMs (up to 20 Mpps with short frame). However, as VALE is developed as a small extension of the netmap module, both QEMU and KVM hypervisors have to be modified for accommodating the new network backend.

**OvS-DPDK**. OvS-DPDK is a form of accelerated OvS with DPDK datapath support, by taking advantage of the DPDK libraries to bypass the host kernel. It appears like creating a user-space vSwitch on the host by using DPDK PMD driver. As a result, OvS-DPDK can achieve up to 10 times performance improvement than native OvS.

**OvS.** OvS is an open source software switch and usually served as a virtual switch in a virtualized environment residing on the hypervisor. OvS nearly supports all L2-L3 network switches such as NetFlow and sFlow. The original intention of OvS is not for speeding up packet processing but for easing the management and configuration of the virtual networks. While OvS uses Linux kernel networking to switch packets between VMs, the performance of native OvS is often unsatisfactory (the performance can be as much as 50 times worse than that of bare metal environment).

**BESS.** BESS is a modular framework for software switches to overcome the severe contradiction between limited NIC abilities and dynamic demands from the users. It allows developers to flexibly add NIC features in software while incurring negligible performance overhead. Borrowing the basic concept from Click, BESS makes it possible for a user to customize the packet processing by using a number of modules. When connecting two modules, a user can create a traffic class. For

delivering packets between two modules, the user then assigns a dedicated core where the traffic class runs as a unique thread. BESS can achieve multiple-10G performance even on a single core.

**Click.** Click is a very popular software router that can be configured in a flexible and modular way. A click router consists of multiple elements, each of which processes packets to implement a single router function [140]. It is very easy to extend Click due to its modularized design. Except for routing, Click can also be used for rapid prototyping and new protocol development. Great efforts have been paid by researchers to improve the performance of Click, such as RouteBricks [28], DoubleClick [76] and FastClick [10].

Obviously, each software framework has its advantages and disadvantages. For instance, pollingbased approaches such as DPDK obtain desired performance at the cost of high CPU resource consumption, while interrupt-driven frameworks such as netmap need large batch sizes, which can also harm performance like latency [153]. Gallenmüller et al. [38] present a comprehensive survey of the state-of-the-art high-performance packet I/O frameworks. They make a comparison among DPDK, netmap and PF\_RING in representative packet forwarding scenarios. Hence, they reveal the impacts of caching and establish a model to evaluate the performance of the three frameworks. Besides, although there may exist other similar frameworks, we focus on the frameworks above since we regard them as the most relevant ones.

# 3.2 Popular Hardware

To achieve high performance, another popular method resorts to employing popular hardware such as network processor units (NPUs), graphics processing units (GPUs), field programmable gate arrays (FPGAs) and smart NICs (sNICs) for NFV acceleration. A common practice is to offload NF processing from the host to hardware, then NFs can perform much faster than when they are executed on a general-purpose CPU. In contrast to special hardware such as application specific integrated circuits (ASICs), these pieces of hardware have many advantages. Table 3 presents a brief introduction to the hardware that can be employed for NFV acceleration.

**NPU.** NPU is a programmable and general-purpose processor specially designed for packet processing. It adopts multi-core architecture with parallel processing capability, high-speed interface and I/O capacity, which is commonly used in the communication field to perform packet processing, protocol analysis, route lookup, voice/data convergence, etc. The execution logic inside an NPU depends on the software loaded during the runtime, which is developed using a dedicated instruction set, i.e., microcode. NPUs are used in the manufacture of a variety of network devices such as software routers, switches, firewalls and session border controllers (SBCs).

**GPU.** The original role of GPU is for graphics rendering. Now GPU has been widely used to supplement a CPU and accelerate many compute- and memory-intensive applications due to its extreme thread-level parallelism, which makes it very suitable for packet processing. GPU can be used for various NFs such as software routers [52], IPsec gateways and network intrusion detection systems (NIDSes) [43].

**FPGA.** FPGA contains an array of programmable logic blocks using a large number of gates. These logic blocks can be configured to perform complex functions. Besides, FPGA also includes memory elements to store states and data, and has a large number of parallel cores within an FPGA chip. However, low-level hardware description languages (HDLs) like Verilog and VHDL, have to be used to program FPGA [88], which make the programming efforts to be huge. On this account, high-level synthesis (HLS) tools [20] that allow developers to program FPGA with high-level programming languages [88] are adopted in many FPGA-based solutions.

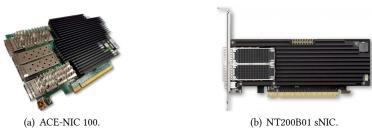

**sNIC.** sNIC is an enhanced NIC which often has its own multi-core processors and an internal switch compared with traditional NICs. A standard OS can run within the sNIC, which makes it possible to offload almost any packet processing functions from CPU, such as security-related applications [98, 124]. Note that some sNICs can be manufactured using other hardware, such as FPGAs [100, 134].

Similarly, different hardware also has its strengths and weaknesses. Though NPU has advantages such as high performance and programmability, its applications are still limited due to the high cost and domain-specific restriction (generally applied to dedicated communication devices). As different

| Hardware | Feature                         | Use in NFV                                                                      |

|----------|---------------------------------|---------------------------------------------------------------------------------|

| NPU      | Programmability                 | Optimized for packet processing in network devices                              |

| GPU      | Massive parallelism             | Improve the throughput of compute- and memory-<br>intensive applications        |

| FPGA     | Reconfiguration                 | Accelerate complex packet processing with high perfor-<br>mance and flexibility |

| sNIC     | Flexibility and programmability | Offload almost any NFs from CPU for processing                                  |

Table 3. Common popular hardware for NFV acceleration.

vendors have different microcode standards for NPUs, developers usually get stuck in building an ecosystem. Though the microcode of some NPUs has supported to be compiled and generated using high-level languages like C, its conversion efficiency is poor. Based on [69], the advantages of GPU for packet processing are vectorization and memory latency hiding when compared to CPU. However, the communication between CPU and GPU introduces latency. The processing of large batches of packets on GPU further increases latency. Moreover, GPUs will no longer have the advantage of a big part of memory bandwidth compared to CPUs under random accesses, as the memory subsystem in GPUs is optimized for adjacent access. Compared with NPU, FPGA is more versatile due to its reconfiguration feature. Furthermore, FPGA is more power-efficient than GPU. In contrast to CPUs or GPUs, the major advantage of FPGA is that it can provide ultra-low latency through the PCIe channel between CPU and FPGA, which is just in the order of nanoseconds. However, the programming complexity of FPGA is non-trivial and hinders the development of this technology for years [8]. For sNICs, they typically have limited total compute and memory capabilities compared to CPUs.

Although there may exist other hardware for NFV acceleration, we focus on the listed hardware above since they appear in the surveyed works most frequently.

Besides, a standard specification called sing-root I/O virtualization (SR-IOV) [82] is commonly used to improve the throughput of NFs. It defines a mechanism to create shared network devices called virtual functions (VFs). This sharing makes a sing I/O device appear to be multiple separate physical devices. By providing independent memory space, interrupts and DMA streams, SR-IOV bypasses the host kernel in data transfer. However, SR-IOV is hardware-dependent since it needs the support of NICs. It also has theoretical limits as a physical device at most supports 256 VFs.

### 4 TAXONOMY AND SURVEY OF ACCELERATION APPROACHES

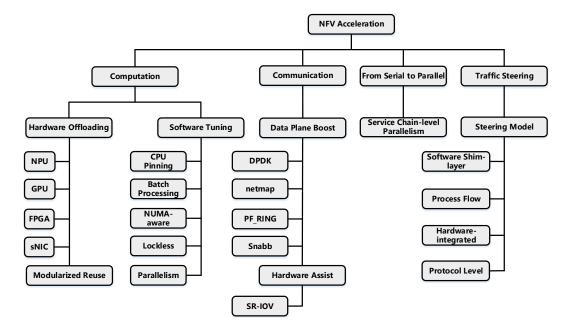

After we carried out a comprehensive investigation of the research efforts in the field of NFV acceleration, we propose a taxonomy for these works according to various acceleration approaches. As illustrated in Figure 3, we classify computation and communication acceleration as two main categories of NFV acceleration, since NFs are usually identified to be compute-intensive (e.g., IPsec gateway) or network-intensive (e.g., network address translation). Many solutions are proposed to accelerate these NFs with strict performance requirements. Recently, some works [132, 156] in the literature have studied how to improve NFV performance through network function parallelism, which are different from previous acceleration approaches. Hence we add this acceleration technology as an independent category in order to draw more attention. Besides, packet steering happens repeatedly in every step of a service chain to handle a packet and can cause severe inter-core transfers without proper acceleration. Therefore, we also add the packet steering acceleration as a separate category, which is very crucial for improving service chain performance in NFV.

For some categories, we classify them into more subcategories based on the specific means they employ. Specifically, the taxonomy contains the following aspects of NFV acceleration:

• **Computation Acceleration**: no matter which means to adopt, either with hardware offloading, software tuning or modularized reuse in NFs, the essence of the approaches is to reduce CPU resource consumption. According to this purpose, we classify those approaches into this category. (See Section 4.1)

Fig. 3. Taxonomy of the surveyed NFV acceleration approaches.

- **Communication Acceleration**: in this category, the approaches generally exploit high performance I/O frameworks and I/O passthrough technology such as SR-IOV. The primary purpose is to speed up packet processing and improve throughput. (See Section 4.2)

- From Serial to Parallel Acceleration: we treat this category as NFV-specific, since it is optimized for decreasing latency by running some NFs of a service chain in parallel without violating NF dependencies. (See Section 4.3)

- **Traffic Steering Acceleration**: the purpose of this category is to decrease inter-core communications or deal with more complex situations in traffic steering, by utilizing efficient steering models. Considering that many NFs are stateful, this form of acceleration is vital to achieving high-performance service chains. (See Section 4.4)

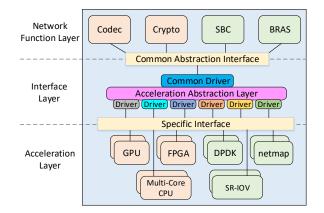

Note that the classified characteristics of NFV acceleration approaches might be correlative, particularly the subcategories between computation and communication acceleration, and between communication and traffic steering acceleration. For instance, the benefits of software tuning can be multifold. On one hand, tuning techniques such as data prefetching and batch processing of packets ensure rapid NF computation in processors. On the other hand, techniques such as zero-copy packet delivery using shared memory enable fast communication between NFs. The branches of a certain subcategory can also be correlative, while we just highlight the dominant features. For example, some sNICs are manufactured using FPGAs [100, 134]. Besides, other techniques such as keeping the cache line aligned to avoid packet transfer among multiple cores, conform to the idea of traffic steering acceleration. In this taxonomy, we just classify software tuning in computation acceleration as a representative. Furthermore, our taxonomy also considers different levels of NFV acceleration, from an NF block [17] abstracted from a monolithic NF to a service chain that connects multiple NFs. Other studies on NFV acceleration [18, 21, 86] provide a rather coarse-grained taxonomy or focus on only one aspect. Specifically, Bronstein et al. [18] focus on hardware acceleration and advocate solving the compatibility problem by providing an abstraction to hide the complexity of the implementation. Chatras et al. [21] target on NF's portability across different platforms for delivering high performance, and classify acceleration solutions into software and hardware acceleration. Lettieri et al. [86] just focus on the NFV data-path. By contrast, our work is more comprehensive and covers the contents of the three studies above.

Besides, energy consumption should not be sacrificed in accelerating NFV. We would not discuss it further with few related works. Data traffic demands (e.g., synthesized or adversarial workloads) are of great importance in benchmarking NF performance, see Section 6.2 for details.

In the subsequent sections (from Section 4.1 to Section 4.4), we introduce and discuss the surveyed works according to this taxonomy. In Section 4.5, we briefly summarize and compare these works.

#### 4.1 Computation Acceleration

Computation acceleration is often used to enable high performance for compute-intensive NFs, such as encryption and transcoding, which require significant CPU resources and involve complex CPU calculation. There are three types of methods in computation acceleration literature, namely, hardware offloading, software tuning and modularized reuse.

4.1.1 Hardware Offloading. The most common approach in computation acceleration is to utilize specialized hardware, which is referred to as look-aside accelerator in [44]. Moving NFs to accelerator hardware significantly saves CPU resources, which could be spent in other revenue-generated applications. Hardware offloading solutions have long been a research topic in developing high-performance applications. In the following, we review these works according to the hardware they employ.

**NPU-based solutions.** NPUs have been used for improving the performance of some specific NFs such as software routers and switches. In this respect, NP-Click [126] is proposed to close the gap between the ease of implementation and efficient implementation. NP-Click is based on Click and provides a programming model for the Intel IXP1200 network processor. The evaluation results on two applications (IPv4 packet forwarding and DiffServ interior node) demonstrate that NP-Click achieves very good performance. Ferkouss et al. [35] implement a high-performance OpenFlow [95] switch on EZchip NP4 network processor. As OpenFlow is rule-based, the authors leverage the flexibility of the switch by updating the flow entries on the fly. Meanwhile, using recursive flow classification (RFC) helps improve the parallelism of the classification process and better exploit the hardware resources. POF [130] builds a hardware-based prototype with the help of NPU. The goal of POF is to eliminate the dependency from forwarding devices (such as switches) without configuring specific protocols and promote the data plane. POF defines a generic flow instruction set to achieve this goal. By taking advantage of the hardware packet parsing modules in the NPU, the authors believe a POF optimized silicon chip can help improve the performance, thus achieving lower network cost and creating new value by enabling flexible network services.

GPU-based solutions. While GPU has higher computation capability and more sufficient programmability than NPU, PacketShader [52] takes the first step to exploit the power of GPUs in packet processing for developing a software router framework. By processing packets in batch, offloading specific packet processing operations to GPUs and scaling them in parallel, PacketShader achieves remarkable higher throughput compared to the CPU-only implementation, while the flexibility and programmability of a software router are still reserved. NBA [77] is a software-based packet processing framework that enables GPU but hides low-level details. It not only maximally exploits the hardware advances (such as batch processing, NUMA awareness, etc.), but also provides an abstraction layer for GPU offloading and achieves adaptive load balancing between CPU and GPU in various workload conditions. As such, the sample NFs of NBA reach up to 80 Gbps for both IPv4 and IPv6 routers, and to above 30 Gbps for IPsec and IDS. Snap [133] is a Click-based packet processing framework that surpasses previous software routers by exploiting the parallelism provided with GPUs. To make GPU elements easily integrated into a processing pipeline, Snap adds a collection of high-performance extensions to the native Click. To achieve this, the authors introduce a set of techniques, including packet slicing to reduce the consumption of bus bandwidth, and predicted execution to deal with the graph composed of Click elements and schedule packets in a pipeline that can be completed in order. They also accelerate common NFs with a collection of GPU-based elements. The evaluation results show that Snap can forward 44 Mpps with a packet size of 128 bytes, even when using elements to implement NFs such as an IP router, a packet classifier and a string matcher with a full payload. This outperforms the baseline CPU-based Click by nearly four

times. DoubleClick [76] is another Click-based solution that focuses on boosting the performance of Click router by employing I/O and batch processing, including a variety of optimizations for current server architectures. For IPv4 packets with size of 64 bytes, the performance can be improved by nearly 10 times through exploiting these techniques. DoubleClick falls into this category since it adopts PacketShader's packet I/O engine for I/O batching.

To reduce the programming efforts for developing high-performance GPU-based network applications, Vasiliadis et al. [136] present a network traffic processing framework called GASPP, which is elaborated for modern GPUs and well-integrated into a GPU-based prototype. GASPP allows developers to build complex GPU-based NFs in a flexible and efficient manner through hiding complex network processing issues, while providing an interface that shows only the data to NFs. The authors also propose a novel packet scheduling mechanism to avoid redundant data transfer and fully use the GPU and the PCIe bus, for efficient memory sharing between network interfaces and GPU. Other optimization techniques such as zero-copy and batch packet processing are applied to the framework design. Based on the evaluation results, GASPP can obtain multi-gigabit throughput even for some compute-intensive and complex network operations that commonly exist in many NFs. In the case of NF consolidation, GASPP obtains as high as 16.2 times performance improvement compared with single-GPU implementations. There are also many works that focus on specific NFs with GPU acceleration, including Kargus [59], Gnort [135] and MIDeA [137] for intrusion detection, and SSLShader [61] for cryptography.

Besides, GPUNFV [146] also exploits the advantage of GPU that delegates packet processing to GPU threads in great parallel. Different from previous approaches, the authors advocate deploying an entire service chain on GPU, which not only potentially reduces the number of needed GPUs, but also decreases data switching between CPU and GPU. What makes it unique is that it efficiently supports both stateful and stateless NFs, by processing the packets of the same flow on the same GPU threads. The evaluation shows that GPUNFV increases the throughput by more than 2 times, compared to packet processing only with CPU. Besides, the waiting time of CPU is no longer required and GPUNFV can quickly get the optimal batching size of packets with the dynamic sizing.

However, the capacity strength of GPU compared to CPU in speeding up NFs has been questioned in an existing work [69]. They claim that the performance improvement of GPU comes from less memory access latency rather than its fast parallel computing, and applying optimization techniques such as group prefetching and software pipelining to GPU code usually results in more efficient resource utilization than native GPU acceleration. Aiming at this doubt, APUNet [43] proves the efficacy of GPU in accelerating NFs and discovers three facts. First, GPU's computational power makes a critical difference in accelerating many compute-intensive NFs. Second, GPU's acceleration power without data transfer outperforms the optimized CPU code. Third, the capability of PCIe communication hinders the offloading of GPU workload, rather than the capacity of GPU. By adopting integrated GPU in accelerated processing units (APUs) and addressing a few practical challenges, APUNet extracts more computational power from integrated GPU with the help of extensive zero-copy models and massive parallelism. It also achieves low-latency data transfer between CPU and GPU. As a result, APUNet improves the performance of many memory- or compute-intensive NFs such as IPsec gateways, SSL proxy and NIDS by 2.2 times to 4 times. However, the performance improvement is not obvious for simple NFs like IPv4 forwarding.

Although GPUs have demonstrated their power in accelerating NFs, Zhang et al. [149] claim that GPUs still have not been effectively integrated into NFV systems yet. They find GPUs are not fully utilized, data isolation cannot be ensured and great development efforts are required in existing GPU-accelerated NFV systems. Thus, they propose G-NET [149], an NFV system that supports several features such as spatial GPU sharing, GPU scheduling and data isolating in GPU. Specifically, by generalizing the CPU-GPU pipeline, data transfer and multi-threading, G-NET provides an abstraction for developing NFs. Therefore, software developers simply need to implement a few specific-purpose NFs, which can largely reduce the development and implementation costs. Through evaluation with various workloads, G-NET is proved to reduce the latency of an SFC by 44.3% and increase the throughput by 70.8%, as compared with the temporal GPU sharing virtualization method.

FPGA-based solutions. Since FPGA is more versatile than NPU and more power-efficient than GPU, ClickNP [88] chooses to accelerate NFs using FPGAs that are considered to be inexpensive. Generally, it is rather hard to tune the logic and debug the code of FPGA since it is usually programmed with hardware description languages. ClickNP overcomes the programming challenges by implementing it in a modularized fashion, with the help of commercial high-level synthesis tools. By exploiting the massive parallelisms in FPGA with a set of optimization techniques, ClickNP obtains high throughput up to 200 Mpps and ultra-low latency for various types of software NFs. Compared with existing GPU-accelerated and pure CPU-based counterparts, ClickNP not only improves the throughput but also reduces the latency. To further implement rich as well as highperformance NFs besides packet processing functionality, Emu [131] develops a new standard library for NFs on FPGAs, while providing an execution environment that is easy to program and debug. Using Emu, developers can rapidly implement and deploy various NFs by programming FPGAs with a high-level language, while supporting fine-grained debugging and profiling capabilities to monitor the states of NFs at runtime. Compared to Linux native counterparts and native Verilog implementations, the performance of Emu significantly outperforms the former in both latency and throughput, while incurring a negligible overhead compared to the latter.

Considering that FPGA is expensive (compared to general-purpose CPU) and the limited number of building blocks on an FPGA board, it is both resource-demanding and cost-inefficient if the entire NFs are implemented on FPGA. Moreover, employing FPGA to accelerate the whole service chain is inflexible, due to the fact that FPGA has to be reprogrammed when introducing new NFs and the reprogramming time can be hours for tuning the code. To overcome the problems above, Li et al. [91] present a novel framework with CPU-FPGA co-design called dynamic hardware library (DHL), while providing both high performance and flexibility for NFV systems. To achieve this, DHL abstracts accelerator modules in FPGA as a hardware function library and provides a set of programming APIs linked to these accelerator modules. In this way, DHL decouples the hardware development of FPGA accelerator modules and software development of NFs, which enables both hardware developers and software developers to intently apply their expertise. To ensure fast communication between FPGA and CPU while keeping very low latency for NFs, DHL also designs an efficient DMA engine by employing a series of optimizations to improve the efficiency of data transfer. The evaluation results show that DHL can reach high throughput by up to 40 Gbps that is similar with FPGA-only solutions, and only incur latency less than 10 µs, while enjoying the flexibility that is lacking in FPGA-only solutions.

sNIC-based solutions. To offload NFs from host CPUs to sNICs, UNO [84] proposes a generalized NF offloading architecture that is managed by an SDN (software-defined networking) controller, for achieving the maximum resource utilization of both sNIC and host. It is non-trivial to achieve this due to three challenges. First, the sNIC is incapable of hosting all NFs and network switching in it, due to its limited total compute and memory capacities. Second, the CPU-sNIC co-design framework imposes extra bandwidth consumption on account of frequent data transfer between the host architecture and the sNIC. Third, the fact that packets traveling through multiple NFs between the host and the sNIC put great pressure on the controller. To address these challenges, UNO introduces an NF agent which makes the SDN controller unaware of the existence of the sNIC. To intelligently balance the load between the host and sNIC, UNO leverages a mathematical method to decide where an NF should be placed (at the host or on the sNIC). For ease of management, UNO translates rules from the SDN controller into rules that are used for NF traversal between the host and sNIC with OneSwitch of UNO. Experiment results demonstrate that UNO can use less than 8 CPU cores, while reducing the power consumption by 2 times and the management overhead of the SDN controller by more than 50%. Besides, Floem [113], a programming system, also targets at offloading computation to sNIC, while providing programming abstractions to overcome many common problems for developers, such as expression of communication strategies, data consistency and reuse of the code. Floem can accelerate many datacenter applications with sNIC offloading, including key-value store and data analytics, and improve the performance of common NF tasks such as encryption and flow classification.

When NFs on sNICs are overloaded, UNO adopts a naive solution to alleviate this condition by migrating the bottleneck NF that occupies the least sNIC resource. This incurs increased latency of a service chain since packets have to travel through PCIe for two more times. To overcome this problem, Meng et al. [96] propose PAM, the push aside migration solution, to intelligently migrate the right NFs to avoid the hot spot on sNIC. Specifically, they select to migrate NFs that lie on the border between sNIC and CPU, while releasing the resources on sNIC to serve the bottleneck NFs. As a result, extra packet transmissions over PCIe can be avoided. Since it is non-trivial to select the right border NFs for migration, they further propose an effective algorithm to make the migration decisions by establishing a resource model. The evaluation demonstrates that PAM can relieve the hot-spot issue on sNIC, while reducing the latency of a chain of NFs by 18% compared with UNO.

*4.1.2 Software Tuning.* Software tuning refers to a set of optimization techniques in order to achieve high performance. There may exist many tuning techniques in the literature, while we choose to present those common ones including CPU pinning, zero-copy, batch processing, NUMA-aware, lockless and parallelism techniques. Table 4 gives a brief description of these techniques.

Software tuning techniques are widely adopted in many existing works. A representative example is Hyper-Switch [115]. As a scalable software-based virtual switch for virtualization platforms (such as Xen [12]), one of its features is to combine with the advantages of both driver domains and hypervisors, while eliminating the software overheads for achievable I/O performance inherent in hypervisors, without incurring associated memory sharing overheads for packet delivery between VM and the NIC driver. The other feature is a set of optimizations that enable high performance. Specifically, Hyper-Switch removes the costs of hypervisor entries and guest announcements by using state-aware batching of packets, reduces the packet arrival latency by employing preemptive copying, and considers CPU cache locality when using low-overhead techniques to dynamically offload packet processing to idle CPU cores, respectively. All these optimizations yield improved network performance. In the evaluation for measuring the total inter-VM network throughput, Hyper-Switch reaches throughput up to 81 Gbps while it only achieves about 31 Gbps and 47 Gbps on Xen and KVM, respectively.

To eliminate the performance overheads in a virtualized environment such as VMs or containers, NetBricks [108] takes a bold step for building and running NFs in a bare-metal environment while providing the equivalent isolation in software, resembling VMs and containers. By allocating a dedicated CPU core per NF or running an NF chain on a single CPU core, NetBricks shows several to ten times better performance than the case of NFs running on the basis of a VM or container, for both individual NF and NF chain. NetBricks also introduces a novel technique called zerocopy software isolation (ZCSI) and runs each NF chain as a single process to reduce packet I/O cost. To maximize the performance, each NF chain is entirely placed on the same CPU core in NetBricks, while replicating the processing graph across cores for scaling. NetBricks implements run-to-completion (RTC) processing of each packet and round-robin scheduling to schedule packets among processing nodes. In particular, the RTC model used in NetBricks ensures a packet to be continuously processed from the time it enters an NF to the time it exits, which can avoid inter-core transfer and reduce context switching cost so as to improve the performance. Besides, vTurbo [144] offloads a process to a specialized core called turbo core, which is separated from a CPU core with its exclusive time slice. Offloading workload to dedicated turbo core mitigates the influence of VM's regular core access latency. As a result, vTurbo prominently improves application-level performance in terms of network throughput.

Note that some works may belong to different acceleration categories. In terms of computation acceleration, for instance, NetVM [56] applies many low-level software tuning techniques in its system design. Building upon KVM hypervisor and Intel DPDK framework, NetVM inherits several advantages from DPDK. By using huge pages provided by DPDK, NetVM can work in a NUMA-aware manner. When forwarding packets between the VMs and host, NetVM only needs to copy a packet descriptor through the shared memory, while the packet data still stays in huge page without any copy operations. For shared memory management, NetVM achieves lockless memory design by allocating cores to each parallelized queues, so that the context switching for a contested lock can

| Technique        | Idea                                                   | Effect                                              |

|------------------|--------------------------------------------------------|-----------------------------------------------------|

| CPU pinning      | Execute a process (thread) only on the designated CPU  | Maintain processor affinity and increase cache hits |

| Zero-copy        | Do not copy data from one memory area to another       | Save CPU cycles and memory bandwidth                |

| Batch processing | Process multiple packets in batches                    | Reduce the traversals on the PCIe and I/O buses     |

| NUMA-aware       | Enable a CPU accessing its own local memory            | Obtain faster memory access                         |

| Lockless         | Manage shared memory in a lockless fashion             | Avoid synchronization overhead                      |

| Parallelism      | Perform multiple tasks simultaneously at the same time | Increase task processing speed                      |

Table 4. Common software tuning techniques.

be avoided. As a result, though NetVM uses multiple pipelined VMs to compose complex NFs, it still achieves throughput up to 10 Gbps, which improves the throughput by over 2.5 times compared with the performance of SR-IOV. IX [14] is a user-space networking stack that contains several tuning techniques. IX provides a native, zero-copy API, supporting a batch mode for handling packets until they are finished. Namely, for each network processing stage, the data planes of IX execute all packets in batches. This approach amortizes API overheads and results in a good locality of both instruction and data. To support scalability for multi-core architectures, IX exploits multi-queue NICs to consistently hash the incoming packets to specific queues. This removes the synchronization overhead when running multiple NFs in the data plane. We will further discuss IX in Section 4.2.2 for its hardware-assist I/O processing.

In addition, some reviewed works such as DHL (batching) and NetBricks (zero-copy technique) also exploit these tuning ideas to assist them to achieve high performance.

4.1.3 Modularized Reuse. In practice, different NFs often perform the same or similar processing steps on the same packet. These similar steps are referred to as processing blocks in a processing graph, which is abstracted from an NF. Packets will be processed by each block with individual logic unit. Through in-depth inspection, these processing blocks show that they have very simple operations on packets, such as just drop and alert, and also some complicated functionalities such as payload match of packets or decompressing specific packets. Effective reuse of these processing blocks on NF chains yields prominent performance improvement, especially in terms of per-packet latency. We call this type of computation acceleration as modularized reuse.

For this purpose, CoMb [125] first discloses that middleboxes, which are built and managed as standalone devices, incur the inefficiencies in the use of infrastructure hardware resources as well as network management. Therefore, in CoMb, software-centric implementations of middleboxes are re-architected at both device- and network-level, where consolidated middleboxes share the same hardware platform. To achieve software element reuse, CoMb implements low-level processing components for capturing packets, parsing packet headers, reconstructing TCP sessions, etc. Even though running multiple reusable NF modules on the same hardware platform brings challenges on performance isolation, security and fault tolerance, and CoMb has not addressed the implementation challenges (e.g., software architecture, performance optimization, etc.), it still lights the way for modularized reuse in NFV platforms.

Chowdhury et al. [22] follow up the work of CoMb and propose a disaggregated packet processing architecture, named by MicroNF ( $\mu$ NF in short) based on the concept of CoMb. In  $\mu$ NF [22], the authors also demonstrate that monolithic NFs can lead to hardware resource wastage due to the repeated implementation and execution of common functionality in SFCs, such as packet parsing, packet classification, and session state reconstruction.  $\mu$ NF is a flexible service composition architecture that uses reusable, lightweight, independently deployable loosely-coupled components and communication primitives for composing and implementing NFs for SFCs. Performance optimizations including multi-socket NUMA machines and low-latency packet processing functionalities are also implemented in  $\mu$ NF. Through evaluation, the authors verify that  $\mu$ NF-based SFCs outperform monolithic NF based SFCs in throughput with fewer CPU cycles per packet on average. To further deal with the frequent packet transfer and expensive hardware resource consumption in modularized SFC, CoCo [97] provides a performance-aware approach for deploying modularized SFCs. In order to minimize hardware resource consumption and packet transfer cost, Coco compactly consolidates a set of lightweight components on the same VM (i.e., CPU core). Furthermore, instead of scaling out a monolithic NF, Coco only scales out the element which is overloaded, so as to reduce the scaling overhead. The proposed push-aside scaling up mechanism in Coco can effectively avoid occupying new CPU cores and further degrading the performance.

Slick [7] also identifies the potential in implementing custom, fine-grained packet processing blocks that could be reused throughout many NFs. They propose a solution for programming NFs via a central controlling strategy, by writing a high-level control program to determine what processing should be performed and how traffic should be routed to. However, Slick focuses on efficient resource utilization and has scalability issues since its elements cannot be shared within different NFs and only supports software data plane units. Instead, OpenBox [17] presents a software-defined framework for NFs that maximally utilizes modularized reuse acceleration. To manage NFs efficiently, OpenBox totally decouples the control plane from its data plane (where the processing steps are executed) for each NF using a novel protocol, while similar data plane entities are defined as OpenBox Instances (OBIs). The deployment of application logic is under the control of the OpenBox Controller (OBC), which is a centralized control plane. The OBC provides an abstraction layer to specify the NF logic as processing graphs and is responsible for merging multiple NF graphs so that each packet can go through as few blocks as possible. That is, the length of route between input and output blocks of a merged graph is shortest by reusing the software modules across NFs. OpenBox also supports hardware-based OBIs for accelerating data plane processing and customized building blocks in the control plane for developing new NFs. Consequently, OpenBox gains a significant improvement in network performance, while having great flexibility. However, OpenBox mainly deals with the case that a modularized SFC is consisted of repeated elements whose internal rules pertain to different NFs and not conflict with each other.

As a more aggressive variant of OpenBox, SNF [73] synthesizes NF service chains by removing the redundant operations (i.e., packet and I/O operations) for each traffic class. To merge packet processing graphs, SNF employs the technique of graph search and graph set, which can build an equivalent NF with a single read and single write operation for each packet. Thus, it gains much higher performance than a chain with redundant operations, especially the deployment case with longer chains of NFs running on an NFV platform. The limitations of this approach are also obvious [30]. First, SNF is not suitable for every service chain. In other words, not all chains of NFs can be synthesized to an equivalent NF with a single read and single write operation. Second, SNF does not scale on multi-core architectures, which are critical for large scale NF deployment. Finally, the efficiency of SNF relies heavily on the network operator's control and knowledge about the service chain. Inherited from SNF, Metron [72] integrates the benefits of SNF into its system design to eliminate processing redundancy (e.g., inter-core transfers), which achieves a potential L1 cache speed for processing packets. Different from SNF, Metron allows using multiple threads to leverage multiple cores within each NF, while exploiting hardware-based dispatching that processes specific traffic classes to those cores. However, Metron also inherits the limitations of SNF and requires special hardware equipment (e.g., OpenFlow Switches).

While most of the existing systems concentrate on achieving efficient packet processing across a service chain in L2/L3, they fall short in constructing more complex NFs at the transport layer and above. These complex NFs often require additional processing. For instance, if each NF in a chain performs TCP processing, TCP bytestream reconstruction may be performed multiple times, which results in extra resource consumption. To address the problem, a framework called Microboxes [92] is proposed to support transport-layer-and-above (L4-L7) NFs or even end-system NFs like a caching proxy, while consolidating the protocol processing inside a chain to remove